Circuits and System Volume 16, Number 2 Second Quarter 2016 ISSN 1531-636X Special Issue Dedicated to the Memory of Prof. Ernest S. Kuh **IEEE**

# Circuits and Systems

Volume 16, Number 2 Second Quarter 2016

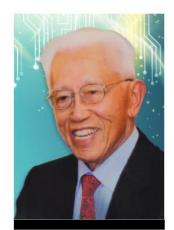

# Special Issue Dedicated to the Memory of Prof. Ernest S. Kuh

#

This paper stresses the importance of applying circuit theory in circuit simulation. Circuit simulation is a combination of circuit theory and numerical analysis. Both the theoretical basis and the numerical algorithms should be robust and accurate to produce reliable and correct results. This communication focuses on the theoretical and practical aspects of circuit equation formulation in the simulation of circuits containing nanodevices.

# From Circuit Theory to Modeling, Large Networks and VLSI Design

Sung-Mo "Steve" Kang

This paper presents a historical review of author's early works influenced by the Circuits and Systems Group at UC Berkeley of which Prof. Ernest S. Kuh was a core member. They range from modeling of nonlinear devices and systems, in particular memristors, design optimization of satellite-based private communication networks to CMOS VLSI design and layout.

# 16 From Circuit Theory, Simulation to SPICE A Matrix Exponential Approach for Time-Domain Analysis of Large-Scale Circuits

Hao Zhuang, Xinyuan Wang, Quan Chen, Pengwen Chen, and Chung-Kuan Cheng SPICE (Simulation Program with Integrated Circuit Emphasis) is a widely used circuit simulation framework for integrated circuit designs. The basic skeleton of SPICE time domain simulation was derived from the versions developed in UC Berkeley during the 1970s. In this paper, we report most recent numerical integration methods to improve traditional SPICE time integration schemes, which are based on linear multistep and low order approximation for the circuit differential equation system. Recently, matrix exponential based time domain simulation algorithms are being developed to address long-term issues in the standard numerical integration methods. We review the related techniques in matrix exponential based approaches and state several distinguished features in challenging simulation problems, such as linear power network analysis and nonlinear circuit system simulation (SPICE<sup>Diago</sup>). We believe that the matrix exponential approaches can shed new light on the research and development of future circuit simulation algorithmic systems.

# 35 Automated Routing for VLSI: Kuh's Group Contributions

# Malgorzata Marek-Sadowska

EDA (Electronic Design Automation) industry is now a multi-billion dollar business and numerous commercial and university tools exist to automatically solve various sub-problems of the IC (integrated circuit) design process. Many of the underlying ideas of the algorithms implemented in those programs originated in Professor Ernest Kuh's research group at UC Berkeley. The objective of this paper is to trace Kuh's group contributions to EDA, to bring attention to this group's many accomplishments in physical design area and to show the effects that the ideas which originated in Kuh's group have had on researchers throughout the years. We limit our attention to routing problems only.

PHOTO OF PROF. KUH COURTESY OF BETTINE KUH BACKGROUND CIRCUIT IMAGE LICENSED BY INGRAM PUBLISHING

REEE Circuits and Systems Magazine (ISSN 1531-636X) (ICDMEN) is published quarterly by the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY, 10016-5997 USA. Responsibility for the contents rests upon the authors and not upon the IEEE, the Society, or its members. IEEE Service Center (for orders, subscriptions, address changes): 445 Hoes Lane, Piscataway, NJ 08854 USA. Telephone: 1 732 981 0060, +1 800 678 4333. Individual copies: IEEE members USS20.00 (first copy only), nonmembers USS163.00 per copy; USS7.00 per member per year (included in Society (es) for each member of the IEEE Circuits and Systems Society. Subscription rates available upon request. Copyright and Reprint Permission: Abstracting is permitted with reddit to the source. Librarles are permitted to photocopy beyond the limits of the U.S. Copyright law for private use of patrons: 1) those post-1977 articles that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923; and 2) pre-1978 articles without fee. For other copying, reprint, or republication permission, write to: Copyrights and Permissions Department, IEEE Service Center, 445 Hoes Lane, Piscataway, NJ 08854 USA. Copyright © 2016 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Periodicals postage paid at New York, NY, and at additional mailing offices. Postmaster: Send address changes to IEEE Circuits and Systems Magazine, IEEE Operations Center, 445 Hoes Lane, Piscataway, NJ, 08854 USA.

Digital Object Identifier 10.1109/MCAS.2016.2550222

(continue

# Features (continued)

# Historical Perspective of System in Package (SiP)

# Wayne Wei-Ming Dai

"Moore Stress" calls for technology and architecture innovation, and System in Package (SiP) is critical to address the challenge. System in Package is a generalization of System on Chip. As such, SiP is a giant chip rather than a miniaturized Printed Circuit Board (PCB). SiP using Wafer Level Package (WLP) enables performance efficient and cost effective integration of DRAM and logic. SiP with Integrated Passive Devices (IPD) provides high quality and low energy platforms for mixed signal and RF circuits. Billions of chips are shipped each year using SiP due to ultra small form factor with very low power consumption for smartphones, smart wearable devices such as smart watches, and Internet of Things (IoT). From editing the book "Multichip Modules" in 1992 to providing leadership for the IEEE Multi-Chip Module Conference (MCMC) from 1992 to 1997, Professor Ernest Kuh made profound contributions to the field of System in Package, particularly in design, analytical methods, and extensively toward CAD tools for SiP. His influence and vision led to the special session on "System in Package" at ASP-DAC in 2000, where the term "System in Package (SiP)" was used in a conference and in publications for the first time and is now widely used in the industry.

# 62 Layout Optimization for Quantum Circuits with Linear Nearest Neighbor Architectures

# Massoud Pedram and Alireza Shafaei

This paper is concerned with the physical design of quantum logic circuits. More precisely, it addresses the problem of minimizing the number of required qubit reorderings (achieved by inserting explicit SWAP gates) when mapping a quantum circuit into a linear nearest neighbor quantum architecture. First, an interaction graph that captures the interaction distances among various qubits in the quantum circuit is constructed. The interaction graph is utilized to partition the quantum circuit into a set of subcircuits such that the number of required qubit reoderings within each subcircuit is provably no more than a given threshold. Next, a Minimum Linear Arrangement problem for each subcircuit is formulated and solved to achieve the minimum number of internal gubit reorderings and determine the subcircuit input and output qubit orderings. Finally, a bubble sort algorithm is repeatedly employed to minimize the number of qubit reorderings that are required between the consecutive subcircuits. Experiments done on various quantum Fourier transform circuits as well as various reversible logic circuits demonstrate the effectiveness of the proposed approach.

# Department

# From the Guest Editors

Scope: Insofar as the technical articles presented in the proposed magazine, the plan is to cover the subject areas represented by the Society's transactions, including: analog, passive, switch capacitor, and digital filters; electronic circuits, networks, graph theory, and RF communication circuits; system theory; discrete, IC, and VISI circuit design: multidimensional circuits and systems; large-scale systems and power networks; nonlinear circuits and systems, wavelets, filter banks, and applicatiors, neural networks, and array computing, circuits and systems for communications, computer-aided network design, digital signal processing, multimedia systems and applications, neural systems and applications, nonlinear circuits and systems, and power electronics and circuits, sensors and micromaching, visual signal processing and communication, and VISI systems and applications. Lastly, the magazine will cover the interests represented by the widespread conference tivily of the IEEE Circuits and Systems Society; In addition to the technical articles, which may be seen as the centerpiece of the start-up plan, we plan also to cover Society administrative activities, as for instance the meetings of the Board of Governors, Society People, as for instance the stories of award winners-fellows, medalists, and so forth, and Places reached by the Society, including readable reports from the Society's conferences around the world.

## **Editor-in-Chief**

Chai Wah Wu T.J. Watson Research Center IBM, USA E-mail: cwwu@us.ibm.com

## Deputy Editor-in-Chief

Alyssa B. Apsel Cornell University, USA

## **Associate Editors**

Pamela Abshire University of Maryland, USA

Ljupco Kocarev

University "Sv. Kiril i Metodij", Macedonia University of California, San Diego, USA

Anthony Kopa

Charles Stark Draper Laboratory, USA

Henry Leung University of Calgary, Canada

Jinhu Lu

Chinese Academy of Sciences, China

Xuan Zhang

Washington University at St. Louis, USA

### **IEEE Periodicals Editorial & Production Services**

Associate Editor — Laura Ambrosio

Senior Art Director - Janet Dudar

Associate Art Directors — Gail A. Schnitzer and Mark Morrissey

Production Coordinator - Theresa L. Smith

Dir. Editorial Services - Dawn Melley

Dir. Production Services - Peter M. Tuohy Advertising Production Mgr. — Felicia Spagnoli

Staff Director,

Publishing Operations — Fran Zappulla Sr. Manager Advertising & Business Development - Mark David

# **Magazine Deadlines**

Final materials for IEEE Circuits and Systems Magazine must be received by the Editor on the following dates:

Issue **Due Date**

First Ouarter December 23 April 1 Second Ouarter Third Ouarter July 1

Fourth Quarter September 15

IEEE prohibits discrimination, harassment, and bullying For more information, visit http://www.ieee.org/web/ aboutus/whatis/policies/p9-26.html.

Digital Object Identifier 10.1109/MCAS.2016.2550223

2 IEEE CIRCUITS AND SYSTEMS MAGAZINE SECOND QUARTER 2016